- 서브 LVDS 판독 및 디코딩 블록

- SPI 기반 센서 구성 모듈

- 센서 구성을 위한 소프트웨어 라이브러리

- 자유 실행 또는 트리거 방식 판독 모드

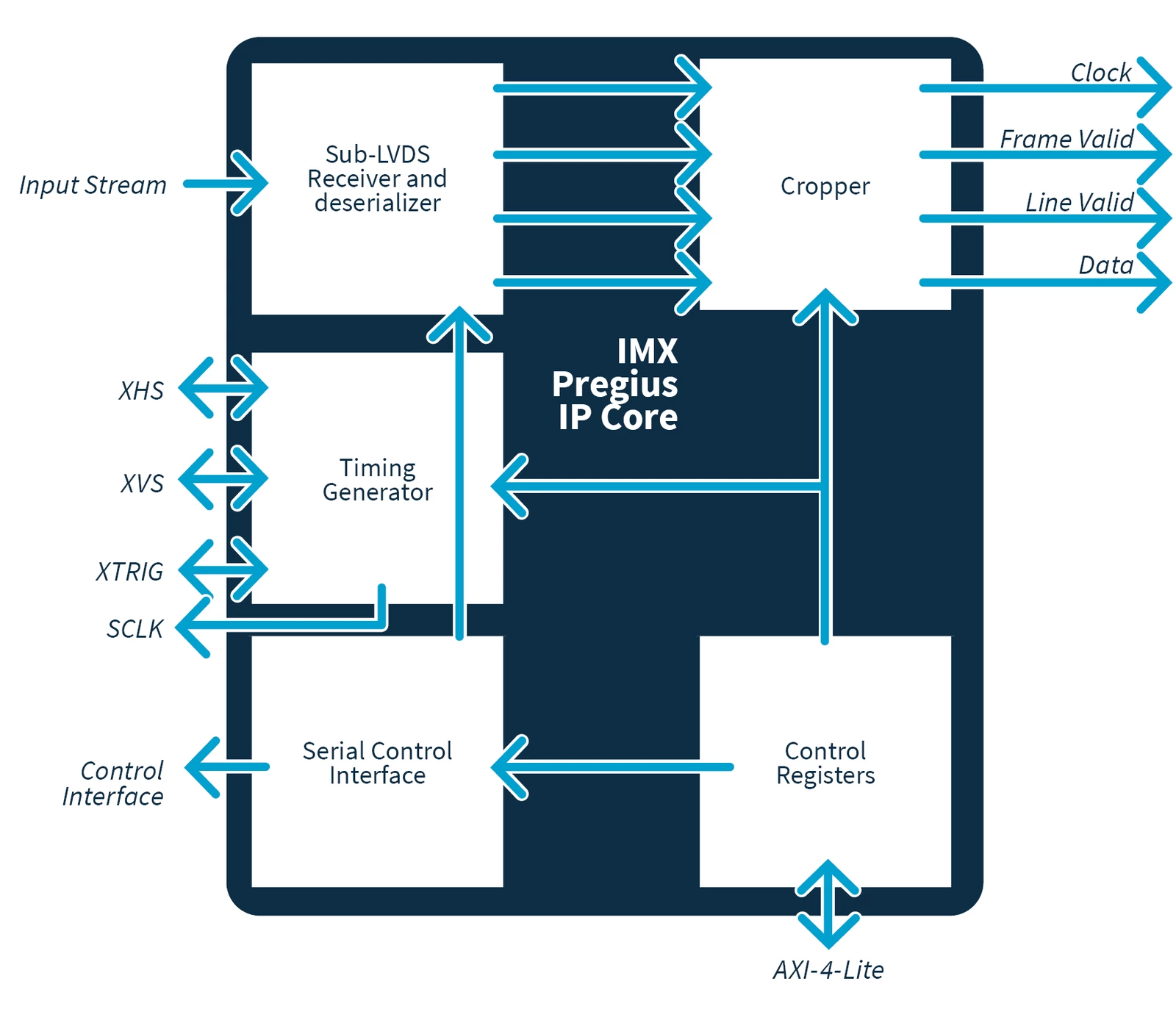

건축

소니의 IMX Pregius는 널리 사용되는 고품질 CMOS 이미지 센서 시리즈입니다. Allied Vision Schongau의 IMX Pregius IP 코어는 이 센서들을 지원하며, 데이터 읽기와 제어 기능을 수행합니다. 이는 Allied Vision Schongau의 MVDK 및 표준 FPGA 평가 키트와 호환되는 FMC 모듈과 함께 합의된 공통 제공 플랫폼에서 실행되는 완전한 기능의 레퍼런스 디자인으로 제공됩니다. 이들을 함께 사용하면 카메라 설계를 손쉽게 수행할 수 있습니다.

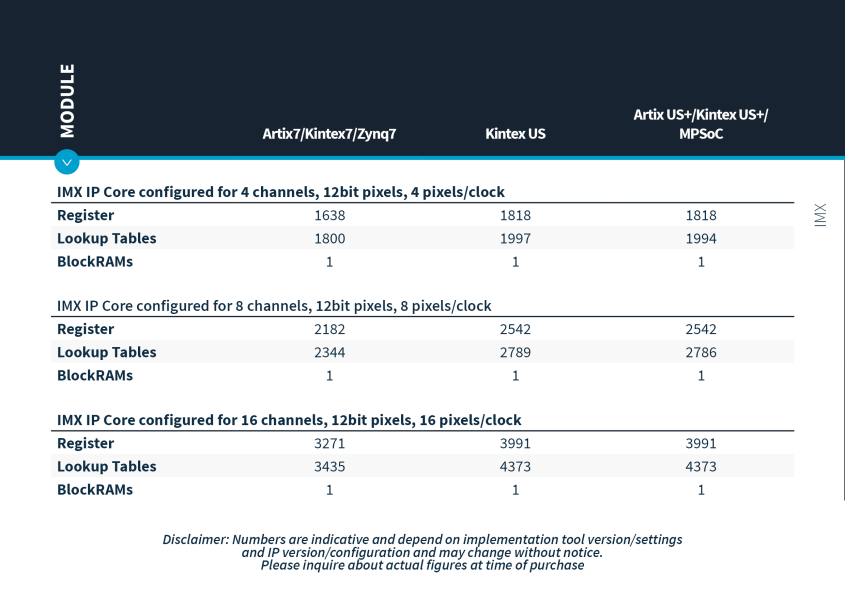

자원 사용량

리소스 사용량 다운로드혜택

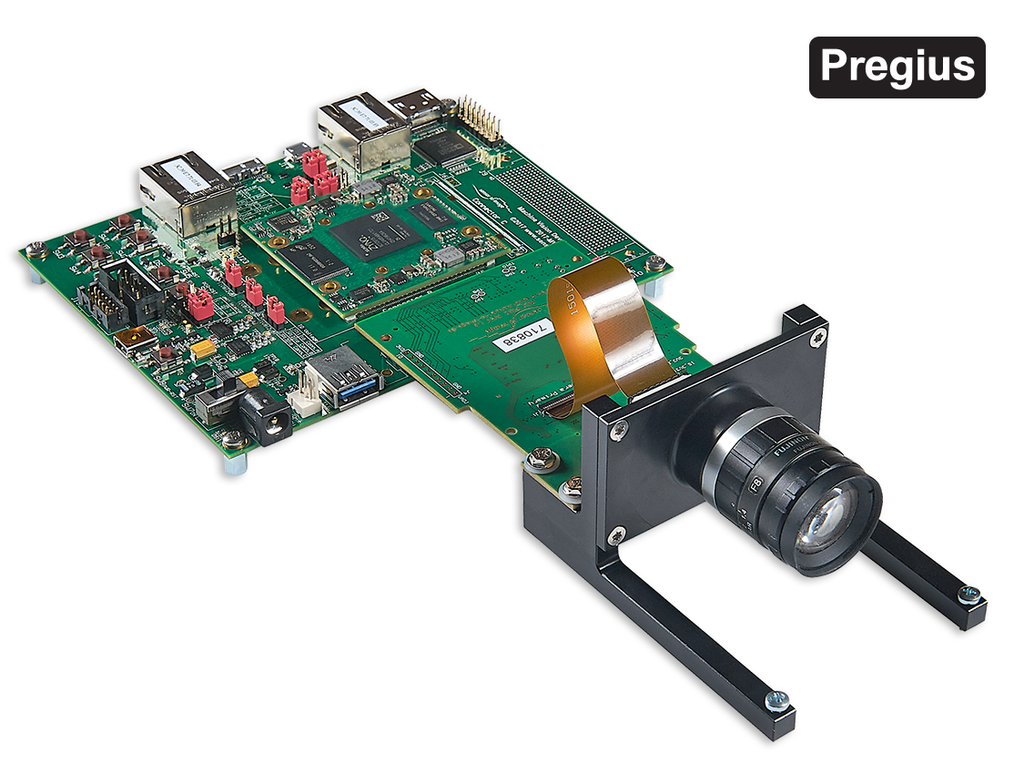

MVDK IMX Pregius 인터페이스 보드

트리거 생성기

IMX 센서 자체는 자유 실행 모드 또는 IP 코어의 타이밍 및 트리거 생성기를 사용하는 종속 모드에서 사용할 수 있습니다. SPI 기반 제어 인터페이스를 통해 올바른 구성 타이밍에 따라 센서 구성이 가능합니다.

제어 레지스터

IP 코어의 기능은 컴파일 시점에 매개변수로 설정하거나, 실행 시점에 AXI-Lite 인터페이스를 사용하는 제어 레지스터로 설정됩니다. C 소프트웨어 라이브러리가 센서와 IP 코어를 구성합니다.

제공된 참조 설계

IP 코어는 GigE Vision 인터페이스를 갖춘 완전한 레퍼런스 디자인과 함께 제공되며, 여기에는 센서와 표준 FPGA 평가 보드 간의 인터페이스를 형성하는 FMC(FPGA 메자닌 카드)가 포함됩니다. FMC 모듈은 FMC-LPC 규격을 준수하며 IMX CMOS 센서가 요구하는 모든 전원 및 레벨 변환을 수행합니다. 라이선스 모델에 따라 IP 코어는 암호화된 VHDL 또는 VHDL 소스 코드 형태로 제공될 수 있습니다. 센서 구성을 위한 소프트웨어 라이브러리가 포함됩니다.

서브LVDS 수신기 및 역직렬화기

SubLVDS 수신기 및 역직렬화기 블록은 센서의 출력 핀에 연결되며 FPGA IO 셀을 사용하여 이미지 스트림을 역직렬화합니다. 이 블록은 FPGA에 매우 의존적이며 현재 AMD FPGA로만 제한됩니다. 병렬 비디오 스트림은 크롭이 가능하며 추가 처리를 위해 카메라 링크(Camera Link)와 유사한 형식으로 제공됩니다.