- 컴팩트한 크기

- 사용자 정의 가능

- AMD 7 시리즈(및 이후 버전) 호환

- Altera Cyclone V 디바이스(및 이후 버전) 호환

- Microchip PolarFire와의 예비 호환성

- 1Gbps부터 10Gbps 이상까지 속도 지원

- 독립형 완전 기능 레퍼런스 디자인으로 제공

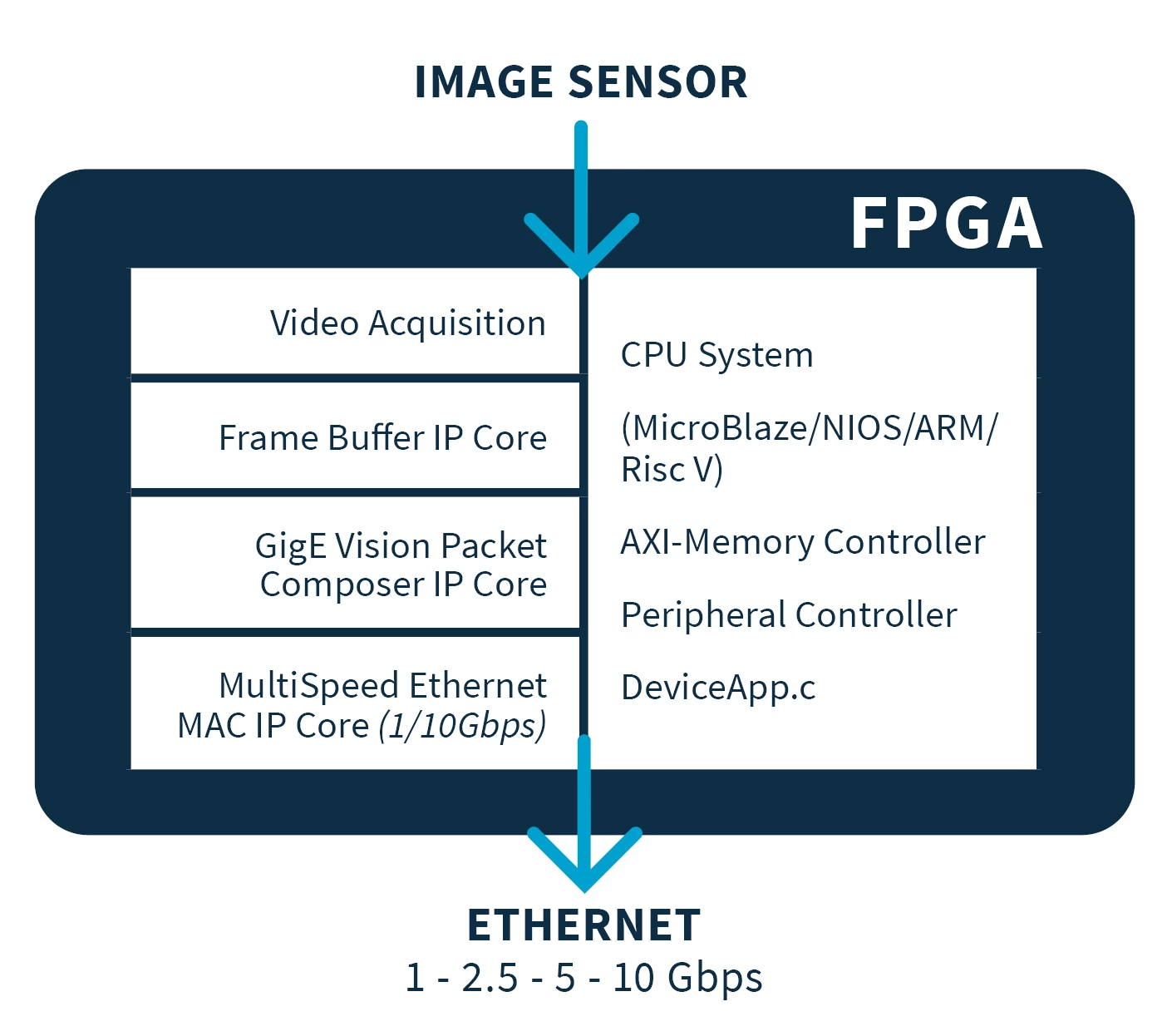

건축

GigE Vision은 잘 알려진 이더넷 기술을 기반으로 한 비전 애플리케이션용 표준 통신 프로토콜입니다. GigE Vision 장치와 TCP/IP 프로토콜 패밀리를 실행하는 PC 간에 손쉬운 인터페이싱을 가능하게 합니다. Sensor to Image는 GigE Vision 인터페이스를 사용하여 FPGA 기반 송신기 제품을 구축하기 위한 일련의 IP 코어와 개발 프레임워크를 제공합니다. GigE Vision의 속도, 특히 1Gbps를 초과하는 속도에서는 송신기가 임베디드 GigE 코어의 고속 FPGA 기반 구현을 필요로 합니다. GigE Vision 코어 세트는 AMD 7 시리즈 디바이스(및 이후 버전), Altera Cyclone V 디바이스(및 이후 버전), Microchip PolarFire와 호환됩니다.

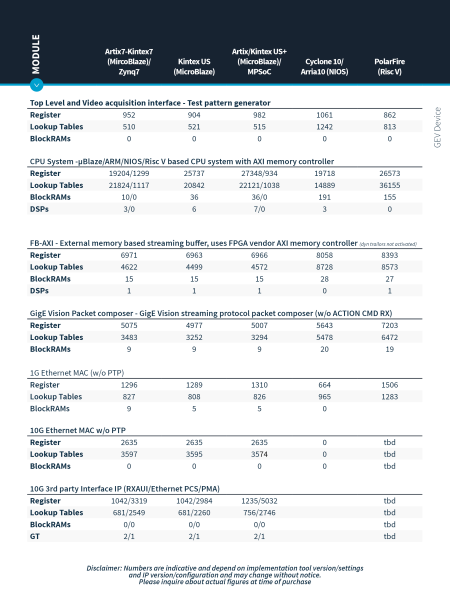

자원 사용량

리소스 사용량 다운로드혜택

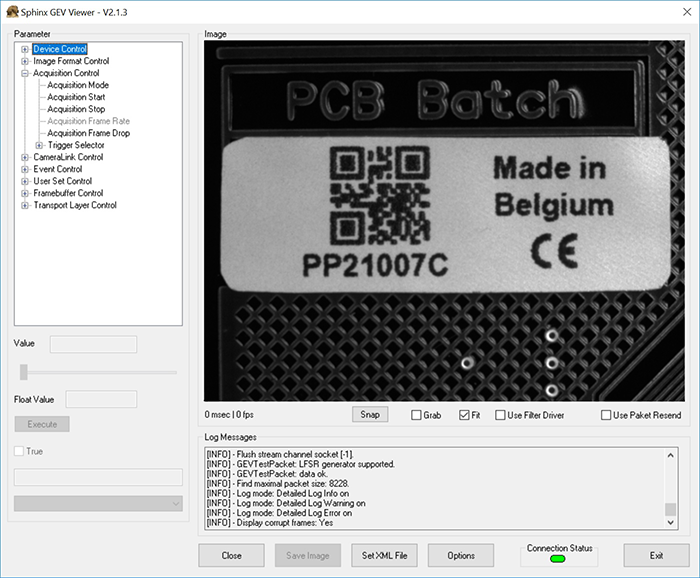

스핑크스 SDK 포함

다양한 기능을 갖춘 소프트웨어 툴킷으로, 최소한의 CPU 리소스를 사용하는 고성능 비디오 애플리케이션을 빠르고 쉽게 설계할 수 있는 구성 요소를 제공합니다. 여기에는 Windows 또는 Linux용 필터 드라이버 및 획득 라이브러리와 함께 GigE Vision/GenICam 호환 뷰어를 포함한 샘플 애플리케이션도 포함됩니다.

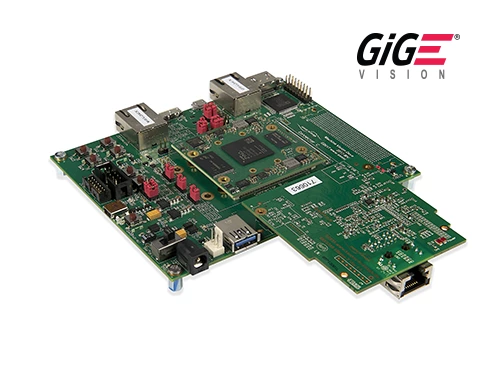

FPGA 개발 키트에 대한 폭넓은 지원

센서 투 이미지의 FPGA IP 코어는 FPGA 개발 키트에 탑재된 완전 작동 가능한 레퍼런스 디자인 형태로 제공됩니다. AMD, Altera, Microchip 등 다양한 업체의 상용 키트를 폭넓게 지원합니다.

GenDC 지원

GigE Vision IP 코어는 강력하고 매우 유연한 GenDC 페이로드 유형을 지원할 수 있는 옵션을 제공합니다. 이는 3D 애플리케이션에서 자주 사용되는 복잡한 데이터 구조를 전송하는 데 유용합니다.

제공된 참조 설계

완전 기능형 레퍼런스 디자인: S2I의 FPGA 솔루션은 FPGA IP 코어와 함께 합의된 공통 플랫폼에서 실행되는 독립형 완전 기능형 레퍼런스 디자인으로 제공됩니다. 이는 개발 시간을 최소화하고 작은 풋프린트에서 최상급 성능을 제공하면서도 설계 커스터마이징을 위한 충분한 유연성을 보장합니다. 센서 투 이미지 코어는 컴팩트하여 FPGA 내에 애플리케이션을 위한 충분한 공간을 확보합니다.

저지연 액션 명령 디코더

GigE Vision IP 코어는 GigE Vision ACTION 명령을 위한 하드웨어 구현 디코더 옵션을 제공합니다. 이를 통해 지연 시간이 짧고 지터가 적은 임시 트리거가 가능합니다.

최상위 설계

IP 코어의 첫 번째 구성 요소는 최상위 설계(Top Level Design)입니다. 이는 외부 하드웨어(이미저, 센서, GigE PHY)와 FPGA 내부 데이터 처리 간의 인터페이스 역할을 합니다. 당사는 이 모듈을 맞춤형 하드웨어에 적용 가능한 VHDL 소스 코드로 제공합니다.

FPGA 통합 CPU

FPGA 통합 CPU 설계(MicroBlaze, NIOS, ARM, Risc V)는 여러 비시간적 네트워크 및 구성 작업에 사용됩니다. 또한 GigE Vision 제어 프로토콜(GVCP)을 구현합니다. 이 소프트웨어는 C 언어로 작성되었으며 고객이 확장할 수 있습니다.

다중 스트림 지원

GigE Vision IP 코어는 단일 링크를 통해 여러 데이터 스트림을 전송하는 옵션을 제공합니다. 이는 서로 관련 없는 데이터를 서로 다른 데이터 소스에서 하나의 케이블을 통해 전송하는 데 유용합니다.

영상 획득 모듈

참조 설계의 영상 획득 모듈은 테스트 패턴 생성기를 통해 카메라를 시뮬레이션합니다. 이 모듈은 VHDL 소스 코드로 제공되며, 최종 카메라 설계에서는 센서 인터페이스 및 픽셀 처리 로직으로 대체되어야 합니다.

사용자 지정 구성

설계의 일부는 바이너리 파일로만 제공됩니다(예: GigE Vision 제어 프로토콜 라이브러리). 반면 다른 부분은 소스 코드로 제공됩니다. 설계 프레임워크에는 필요한 모든 설계 파일과 코어, Vivado 또는 Quartus 프로젝트 파일이 포함됩니다. 이 프레임워크는 구성 가능한 테스트 패턴 생성기를 갖춘 GigE Vision 카메라 시스템으로 구성됩니다. 본 시스템은 상용 평가 보드용 레퍼런스 설계로 제공됩니다. 이 레퍼런스 디자인은 AMD 또는 Altera 개발 도구(제공 범위 외)를 사용합니다.

프레임버퍼

프레임버퍼는 FPGA 벤더별 메모리 컨트롤러와 인터페이스합니다. 프레임버퍼는 프레임 버퍼링 및 이미지 패킷화를 가능하게 합니다. 이는 패킷 재전송 기능을 구현하는 데 필수적입니다. 이 모듈은 일반적으로 외부 메모리를 사용하지만, FPGA의 내부 메모리로도 제한된 기능으로 구현될 수 있습니다.

소프트웨어 라이브러리용 C 소스 코드

GigE Vision IP 코어의 내장 GigE Vision 라이브러리는 선택적으로 소스 코드로 제공될 수 있습니다. 이는 드물게 사용되는 선택적 GigE Vision 기능의 확장을 위해 또는 하드웨어 요구 사항을 더 잘 맞춤화하는 데 유용합니다. 추가 드라이버를 통해 장치에서 Linux를 사용할 수 있습니다.

GigE 이더넷 패킷 생성기

GigE 패킷 컴포저는 GigE Vision 전송 계층에서 요구하는 모든 헤더를 포함한 최종 스트림 패킷을 생성합니다. GigE 패킷 컴포저는 모든 데이터를 이더넷 MAC으로 전송하며 고속 GigE Vision 스트리밍 프로토콜(GVSP)을 구현합니다.

IEEE1588 지원

GigE Vision IP 코어는 외부 IEEE1588 시간 소스와 타임베이스를 동기화할 수 있는 옵션을 제공합니다. 이는 추가 배선 없이 정확한 타이밍 트리거링을 위해 필수적입니다. 외부 시간 소스를 사용할 수 없는 경우 시스템 자체가 시간 소스 역할을 수행할 수 있습니다.

MAC

MAC 구성 요소는 저수준 전송 계층 기술 및 물리 계층과 인터페이스합니다. 1Gbps부터 10Gbps까지 다양한 속도로 제공되며 IEEE1588 프로토콜에 따른 패킷 스탬핑을 지원할 수 있습니다.

FMC 인터페이스 확장

다양한 레퍼런스 보드의 기능을 확장하기 위해, NBaseT를 지원하는 1G 이더넷 및 10G 이더넷용 FMC 카드를 제공합니다.