- MIPI CSI-2 レシーバーおよびデコードブロック

- 設定可能な MIPI レーン数

- AMD D-PHY IP の採用

- 迅速な開発のための動作確認済みリファレンスデザインとして提供

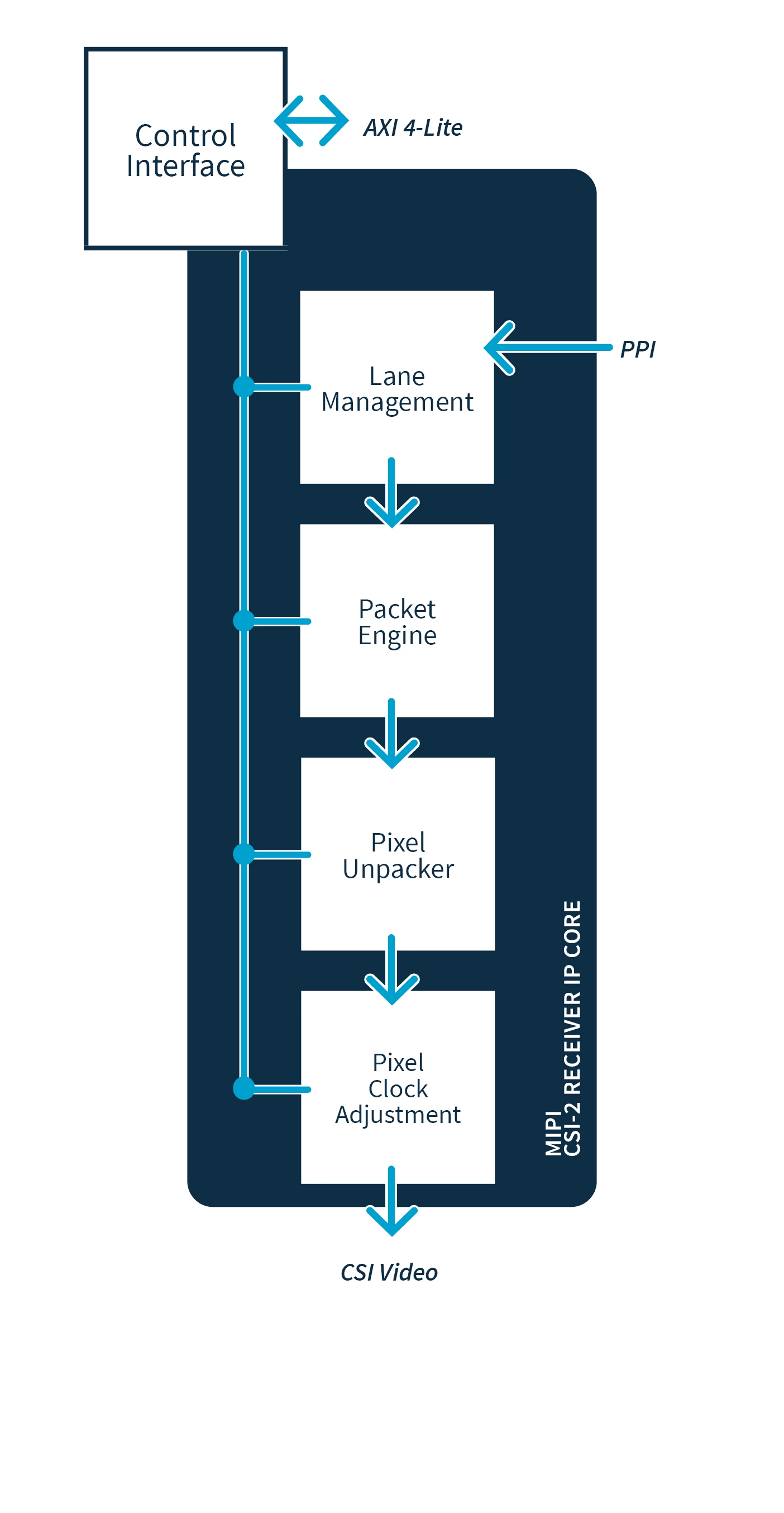

建築

MIPIインターフェースを備えたイメージセンサーは、携帯電話だけでなく産業用および自動車用途にも使用されています。これらの用途では、制御やさらなる処理のためにFPGAが必要となることがよくあります。このIPは、異なるベンダーのMIPIセンサーをFPGAに接続するのに役立ちます。このIPは、FPGAベンダーから一般的に入手可能な既存のD-PHY実装に依存しています。 本IPは、合意された共通提供プラットフォーム上で動作する完全機能のリファレンスデザインとして提供されます。これにはS2IのMVDKおよび標準FPGA評価キットと互換性のあるMIPI FMCモジュールが含まれます。これらを組み合わせることで、カメラ設計を容易に行うことが可能です。

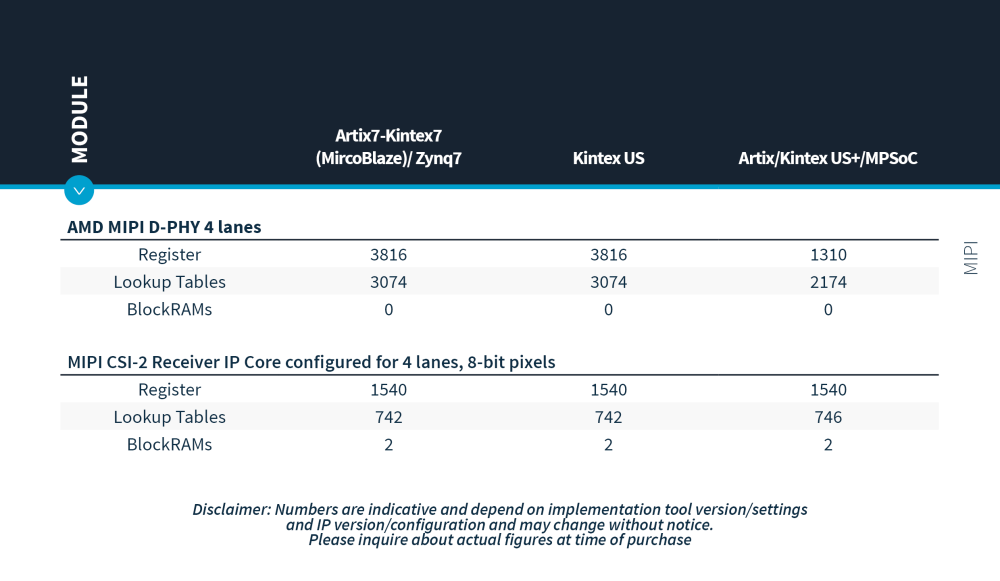

リソース使用量

リソース使用量のダウンロードメリット

MVDK MIPI CSI-2インターフェースボード

主な特徴

- FPGA技術に依存しない

- 異なるD-PHY実装に接続するためのPPIインターフェース

- 1、2、または4のデータレーンに設定可能

- 任意のレーンレート(使用するFPGAによって制限される)

- RAW8、RAW10、RAW12、RAW14、RAW16 標準MIPIデータタイプ

- 組み込みデータデコード

- ピクセルアンパックなしの再順序化バイトストリームの直接出力

- AXI4-Liteスレーブ制御インターフェース

配送

IPコアは、Zynq7またはUltrascale+ FPGAとIMX MIPI FMCモジュールを搭載したS2IのMVDK向け完全なリファレンスデザインと共に提供されます。物理インターフェースはAMD D-PHYコアによって抽象化されているため、例えば7シリーズAMD FPGAなどの他のFPGAプラットフォームへの設計移植が容易です。

利用可能なモジュール

MIPI CSI-2 レシーバー IPコアは暗号化された VHDL 形式で提供されます。オプションで VHDL ソースコードとしても入手可能です。AMD Artix7、Kintex7、Zynq7 および Ultrascale+ FPGA と互換性があります。MIPI CSI-2 レシーバー IPソフトウェアライブラリはオブジェクトファイル形式で提供されます。オプションで C ソースコードとしても入手可能です。