- AMD 7シリーズ(およびそれ以降)に対応

- Altera Cyclone 10デバイス(およびそれ以降)に対応

- コンパクト

- カスタマイズ可能

- 1 Gbpsから100 Gbpsまでの速度をサポート

- 動作するリファレンスデザインとして提供

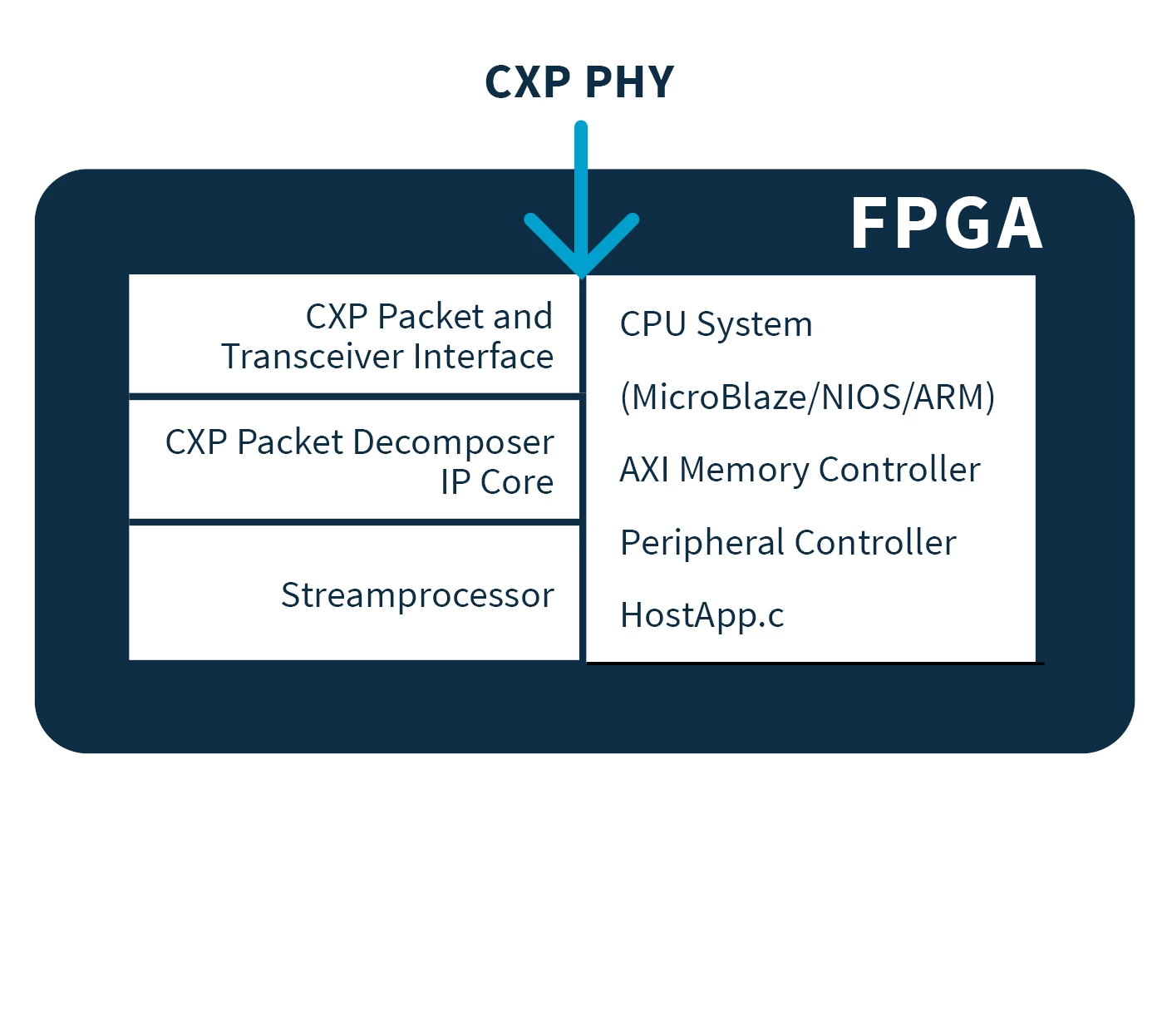

建築

CoaXPress(CXP)は、広く使用されている同軸ケーブルを基盤とした、ビジョンアプリケーション向けの標準通信プロトコルです。カメラとフレームグラバー、あるいは組み込みプロセッサ間の容易なインターフェースを可能にし、GenICamソフトウェア標準をサポートします。 Sensor to Imageは、CoaXPressインターフェースを用いたFPGAベースのレシーバー構築のための一連のIPコアと開発フレームワークを提供します。CXPの高速性により、レシーバーには組み込みトランシーバーを用いた高速FPGAベースのCXPコア実装が求められます。CXPホストコアはAMDおよびAlteraデバイスと互換性があります。

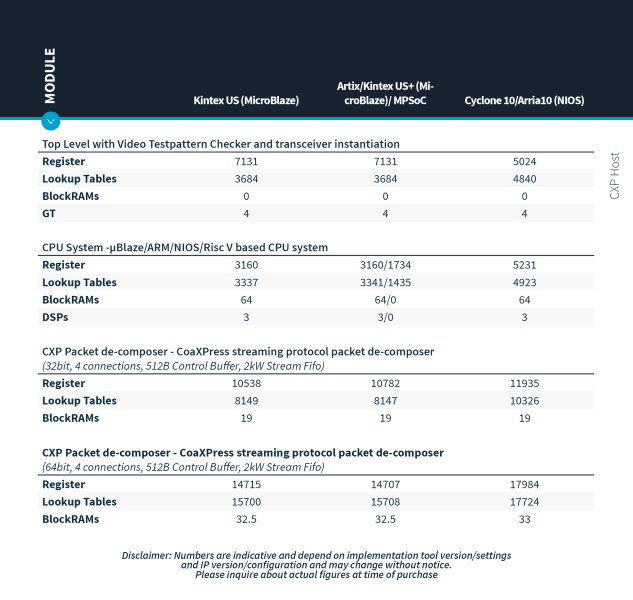

リソース使用量

リソース使用量のダウンロードメリット

MVDK CoaXPress用マシンビジョン開発キット

Sensor to Image MVDK開発キットは、マシンビジョンアプリケーション向けの柔軟な評価プラットフォームです。AlteraおよびAMD FPGAを搭載した各種Enclustra FPGAモジュール向けに、CoaXPressホストおよびデバイスのリファレンスデザインをサポートします。

光ファイバー経由のCoaXPress

光ファイバーケーブルに対応する独立したCoaXPress-over-Fiber-Bridge-IP-Coreが利用可能です。これにより、長距離伝送、高速伝送、または過酷な環境下での運用が可能となります。

提供されたリファレンス設計

完全機能リファレンス設計:S2IのFPGAソリューションは、合意された共通プラットフォーム上で動作するFPGA IPコアと共に、自己完結型の完全機能リファレンス設計として提供されます。これにより開発時間を最小限に抑え、小さなフットプリントで最高水準の性能を実現すると同時に、設計のカスタマイズに十分な柔軟性を確保します。Sensor to Imageコアはコンパクトなため、FPGA内にアプリケーション用の十分なスペースを確保できます。

FPGA統合CPU

CXPデバイス/ホストコアとの連携において、複数の非時間依存制御および設定タスクにはFPGA内蔵CPU(MicroBlaze、NIOS、ARM、Risc V)が使用されます。このソフトウェアはC言語で記述されており、顧客による容易な拡張が可能です。

トップレベルデザイン

IPコアの最初の構成要素はトップレベル設計です。これは外部ハードウェア(イメージャ、センサー、CXP PHY)とFPGA内部のデータ処理間のインターフェースとなります。このモジュールはカスタムハードウェアに適応可能なVHDLソースコードとして提供します。

CXPパケット分解器

CXP制御インターフェースは、CXP制御チャネルの全データを送受信します。外部CXPカメラはこのチャネルを介して制御されます。CXPストリーミングインターフェースはカメラからの全データをデコードし、AXIストリームとして出力します。このストリームはさらなる処理に使用できます。 CXPパケットデコンポーザーは、FPGAトランシーバーへの高速インターフェースを実装するCXPトランスポート層コントローラーと通信します。IPコアは、最適なリソース対性能比を実現するため、32ビット幅または64ビット幅のデータパスで利用可能です。64ビットデータパスにより、このIPはCXP-25に対応しています。

ストリーム処理モジュール

ビデオ処理の例として、リファレンス設計には簡易表示ユニットまたはパターンチェッカーモジュールが付属しており、CXPパケットデコンポーザーユニットのビデオストリーム出力の使用例を示しています。

FMCインターフェース拡張機能

各種リファレンスボードの機能拡張のため、追加インターフェースを提供するFMC(FPGAメザニンカード)を設計しました。MicrochipまたはMacomチップセットを搭載したCXP-6およびCXP-12対応ハードウェア用ボードを提供しています。