- Kompatibel mit AMD 7 Series (und neuer)

- Kompatibel mit Altera Cyclone V-Geräten (und neuer)

- Kompakt

- Anpassbar

- Lieferung als funktionsfähiges Referenzdesign

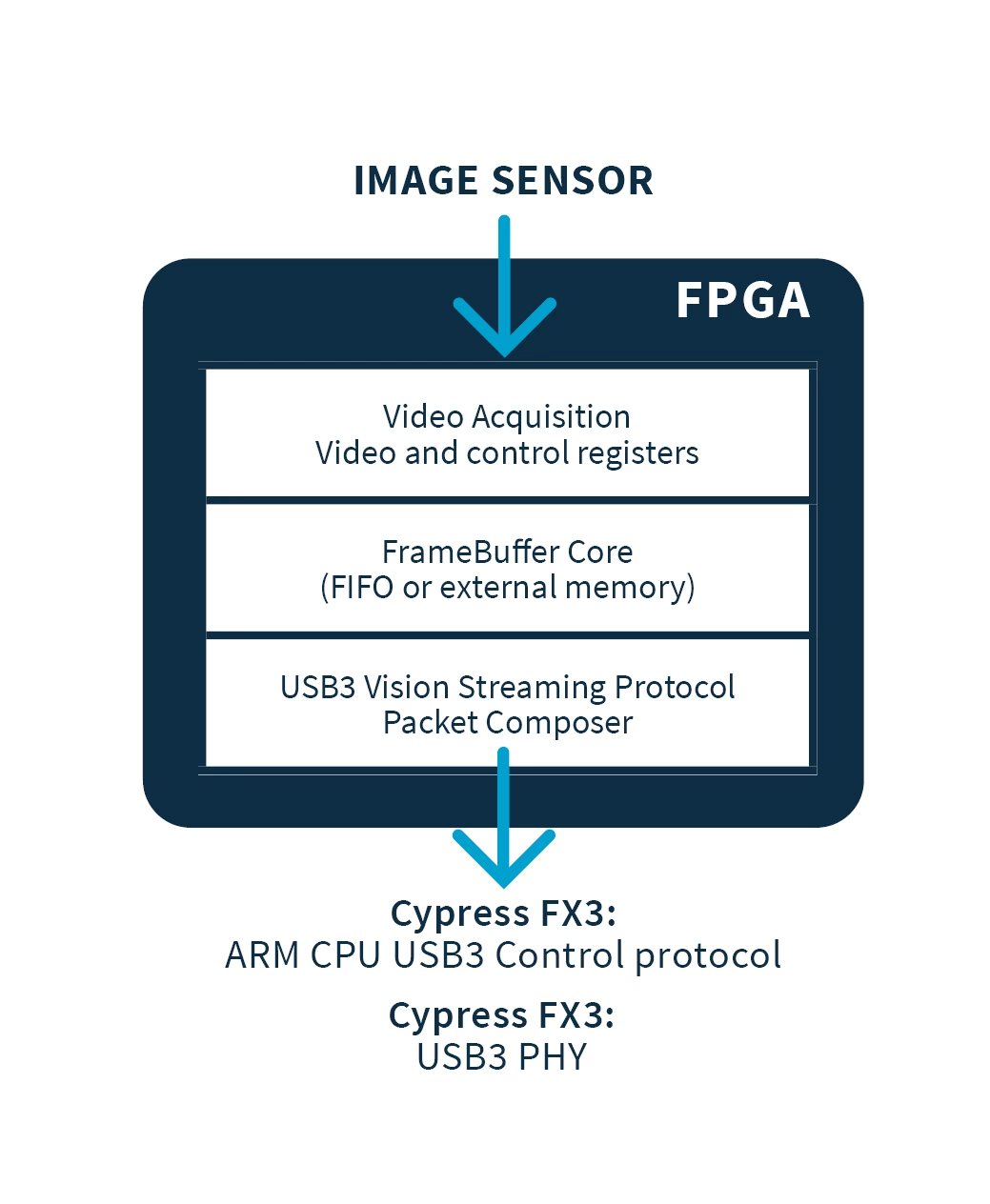

Architektur

USB3 Vision ist ein Standard-Kommunikationsprotokoll für Bildverarbeitungsanwendungen, das auf der weit verbreiteten USB 3.0-Schnittstelle basiert. Da das Protokoll standardisiert ist und GenICam unterstützt, ermöglicht es eine einfache Verbindung zwischen Kameras und PCs. Sensor to Image bietet eine Reihe von IP Cores und ein Entwicklungsframework für die Erstellung von FPGA-basierten Produkten unter Verwendung der USB3 Vision-Schnittstelle. Aufgrund der Geschwindigkeit von USB3 Vision erfordern Sender und Empfänger eine schnelle FPGA-basierte Implementierung des eingebetteten USB-Cores. USB3 Vision IP Cores sind kompatibel mit Geräten der AMD 7-Serie (und neuer) und Altera Cyclone V-Geräten (und neuer).

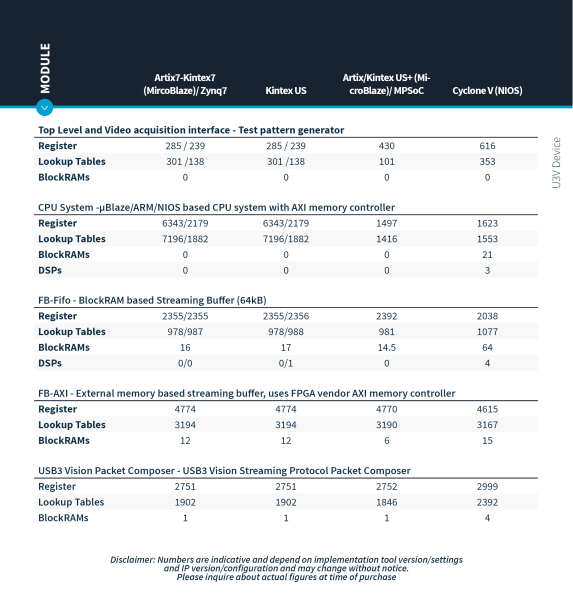

Ressourcenverbrauch

Ressourcenverbrauch herunterladenVorteile

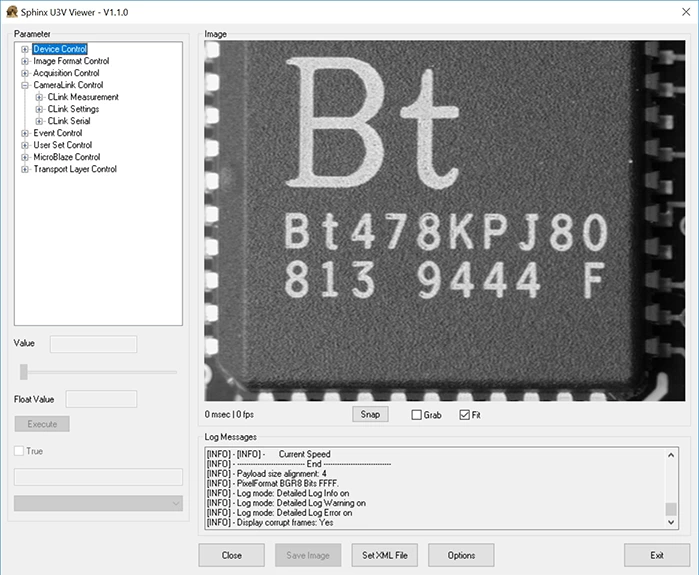

Sphinx SDK enthalten

Sphinx ist ein funktionsreiches Software-Toolkit, das die Bausteine für die schnelle und einfache Entwicklung leistungsstarker Videoanwendungen mit minimalem CPU-Ressourcenverbrauch bereitstellt. Das Toolkit umfasst außerdem einen USB3 Vision-Software Treiber und eine Erfassungsbibliothek für Windows oder Linux sowie Beispielanwendungen, darunter einen USB3 Vision/Genicam-kompatiblen Viewer.

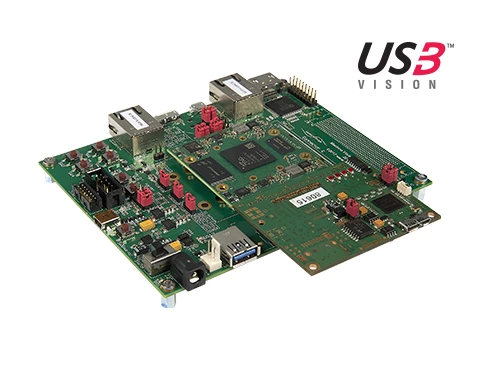

MVDK Machine Vision Development Kit für USB3 Vision

Das MVDK-Entwicklungskit von Sensor to Image ist eine flexible Evaluierungsplattform für Bildverarbeitungsanwendungen. Es unterstützt USB3 Vision-Gerätekonstruktionen für verschiedene Enclustra-FPGA-Module mit Altera- und AMD-FPGAs.

C-Quellcode für Softwarebibliothek

Der USB3 Vision IP Core bietet die Option für den Quellcode der eingebetteten USB3 Vision-Bibliothek, die auf dem Cypress FX3 USB-Controller läuft. Dies ist nützlich, um die Funktionalität für selten genutzte optionale USB3 Vision-Funktionen zu erweitern oder die Hardwareanforderungen besser anzupassen.

Mitgeliefertes Referenzdesign

Die USB3 Vision FPGA-Lösung von S2I wird als voll funktionsfähiges Referenzdesign zusammen mit FPGA-IP-Cores geliefert. Dies minimiert die Entwicklungszeit und ermöglicht eine erstklassige Leistung bei geringem Platzbedarf, während gleichzeitig genügend Flexibilität für die Anpassung des Designs bleibt. Die Sensor-to-Image-Kerne sind kompakt und lassen genügend Platz im FPGA für Ihre Anwendung.

Top-Level-Design

Die erste Komponente des IP Cores ist das Top-Level-Design. Es handelt sich dabei um eine Schnittstelle zwischen externer Hardware (Imager, Sensoren, USB3 PHY) und der internen Datenverarbeitung des FPGA. Wir liefern dieses Modul als VHDL-Quellcode, der an kundenspezifische Hardware angepasst werden kann.

Framebuffer-Kern

Ein Frame-Puffer ist mit dem herstellerspezifischen Speichercontroller des FPGA verbunden. Der Frame-Puffer ermöglicht Datenpufferung und Bildpartitionierung. Dieses Modul nutzt in der Regel den internen Speicher des FPGA, alternativ kann jedoch auch externer Speicher verwendet werden, um längere Kommunikationsverzögerungen zwischen Kamera und PC auszugleichen.

Videoerfassungsmodul

Das Videoerfassungsmodul des Referenzdesigns simuliert eine Kamera mit einem Testbildgenerator. Dieses Modul wird als VHDL-Quellcode geliefert, der im endgültigen Kameradesign durch eine Sensorschnittstelle und eine Pixelverarbeitungslogik ersetzt werden muss.

USB3 Vision Streaming Protocol Packet Composer

Der USB3 Vision Streaming Protocol Packet Composer nimmt alle Daten aus der Videoquelle auf und erstellt die USB3 Vision-Streaming-Pakete. Außerdem übernimmt er die gesamte Low-Level-Kommunikation mit dem USB3 PHY (Cypress FX3).

Cypress FX3

Ein Cypress FX3-Chip (mit integrierter ARM-CPU und physikalischer Schnittstelle) wird verwendet, um alle USB3-Initialisierungsroutinen und die Kommunikation über den USB3 Vision-Steuerkanal zu verarbeiten.