- Sub-LVDS-Auslese- und Decodierungsblock

- SPI-basiertes Sensorkonfigurationsmodul

- Softwarebibliothek für die Sensorkonfiguration

- Freilaufender oder getriggerter Auslesemodus

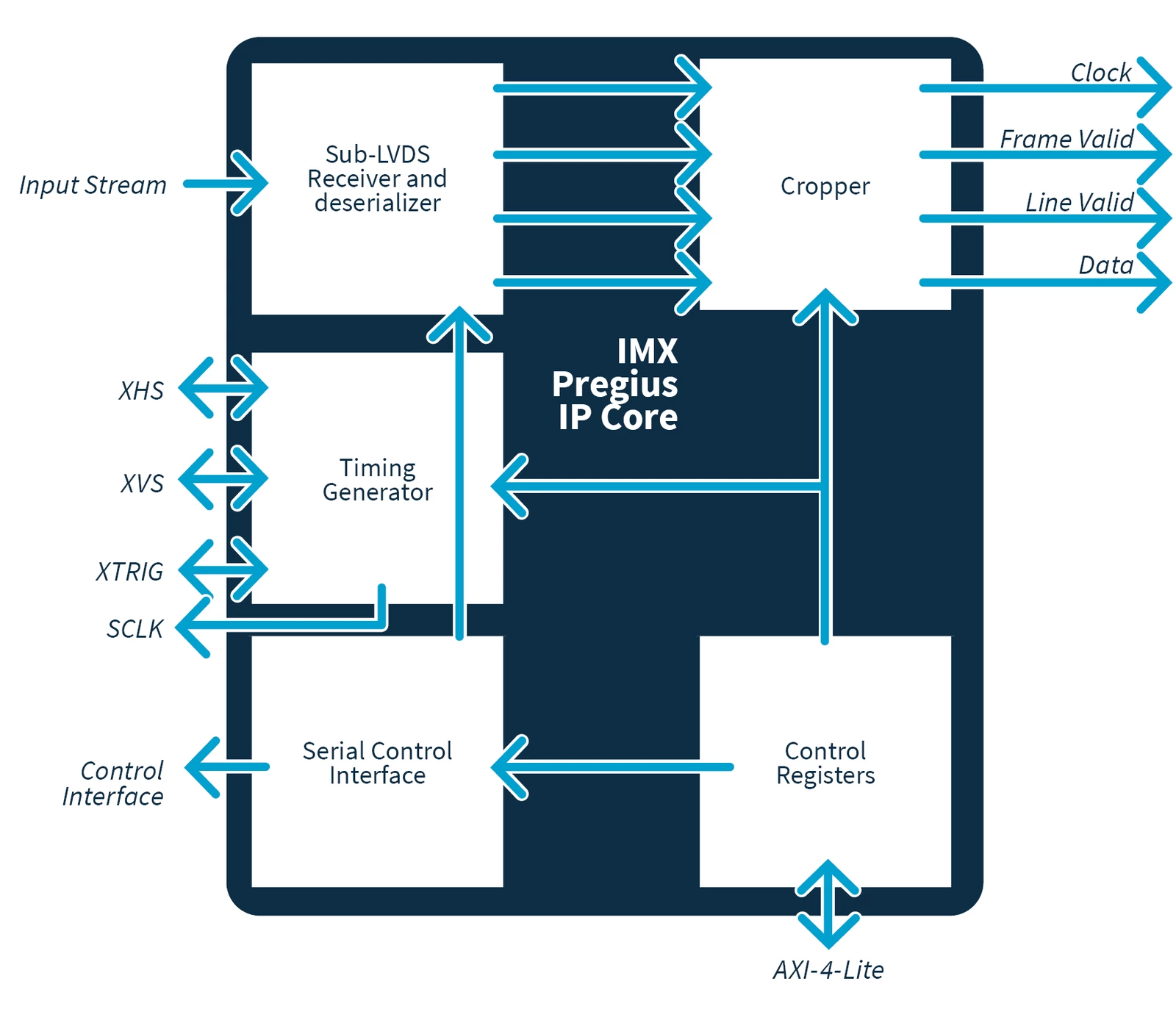

Architektur

Der IMX Pregius von Sony ist eine Serie weit verbreiteter, hochwertiger CMOS-Bildsensoren. Der IMX Pregius IP Core von Allied Vision Schongau unterstützt diese Sensoren, kann ihre Daten lesen und sie steuern. Er wird als voll funktionsfähiges Referenzdesign geliefert, das auf einer vereinbarten gemeinsamen Lieferplattform zusammen mit einem FMC-Modul läuft, das mit dem MVDK von Allied Vision Schongau und Standard-FPGA-Evaluierungskits kompatibel ist. Zusammen bieten sie eine einfache Möglichkeit, eine Kamera zu entwerfen.

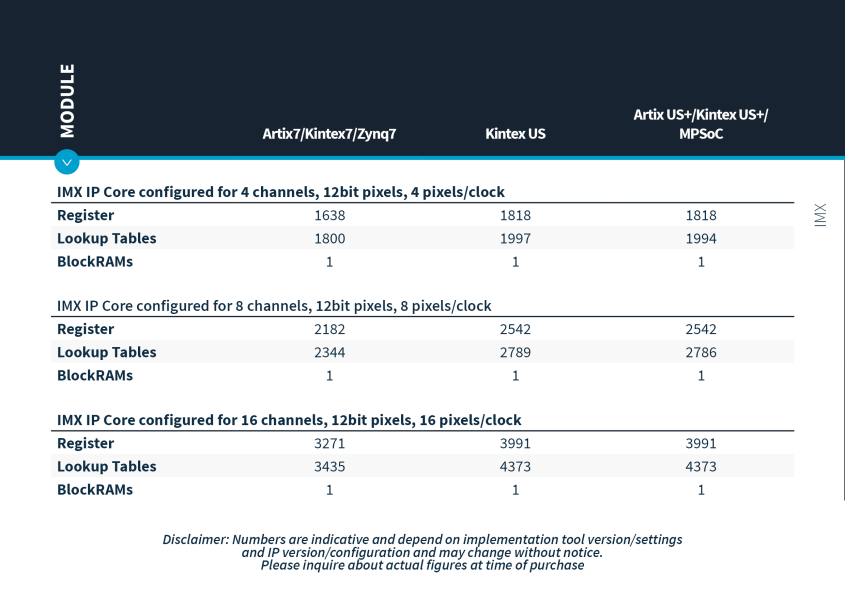

Ressourcenverbrauch

Ressourcenverbrauch herunterladenVorteile

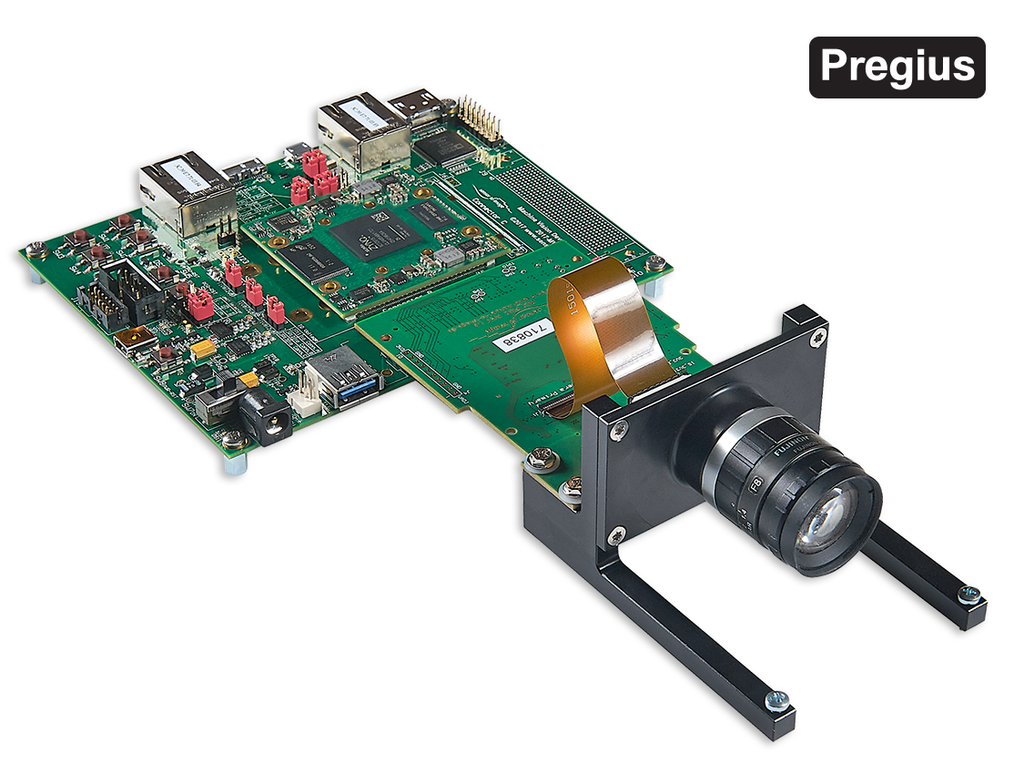

MVDK mit IMX Pregius-Schnittstellenkarte

Triggergenerator

Der IMX-Sensor selbst kann im Freilaufmodus oder im Slave-Modus unter Verwendung des Timing- und Triggergenerators des IP Core verwendet werden. Eine SPI-basierte Steuerschnittstelle ermöglicht die Konfiguration des Sensors gemäß dem korrekten Konfigurations-Timing.

Steuerregister

Die Funktionalität des IP Cores wird entweder durch Parameter zur Kompilierungszeit oder durch Steuerregister unter Verwendung einer AXI-Lite-Schnittstelle zur Laufzeit konfiguriert. Eine C-Softwarebibliothek konfiguriert den Sensor und den IP Core.

Mitgeliefertes Referenzdesign

Der IP Core wird mit einem vollständigen Referenzdesign mit GigE Vision-Schnittstelle geliefert, einschließlich einer FMC (FPGA Mezzanine Card), die die Schnittstelle zwischen dem Sensor und einem Standard-FPGA-Evaluierungsboard bildet. Das FMC-Modul ist FMC-LPC-kompatibel und übernimmt alle vom IMX-CMOS-Sensor benötigten Leistungs- und Pegelanpassungen. Je nach Lizenzmodell kann der IP Core als verschlüsseltes VHDL oder als VHDL-Quellcode geliefert werden. Eine Softwarebibliothek zur Konfiguration des Sensors ist im Lieferumfang enthalten.

SubLVDS-Empfänger und Deserialisierer

Der SubLVDS-Empfänger- und Deserialisierer-Block ist mit den Ausgangspins des Sensors verbunden und nutzt die FPGA-IO-Zellen, um den Bildstrom zu deserialisieren. Dieser Block ist in hohem Maße FPGA-abhängig und derzeit auf AMD-FPGAs beschränkt. Der parallele Videostrom kann zugeschnitten werden und wird zur weiteren Verarbeitung in einem Camera Link-ähnlichen Format dargestellt.